AMD is reportedly planning to introduce a new "3D core" to its U structure, according to a new leak about the forthcoming AMD Zen 7 architecture. What's more, we're apparently not just talking about a massive pool of extra cache here, as seen on recent chips such as the AMD Ryzen 7 9800X3D, but a layer of multiple cache slices sitting directly below an enormous number of U cores, in a structure that could become a standard part of the architecture.

Given that we've yet to see even best gaming U designs. The leak says Zen 7 is expected to launch either in late 2027 or early 2028, so it's at least two and a half years away, but I'm really intrigued about how this new AMD tech could work.

These rumored AMD Zen 7 details were shared by YouTube tech leaker Moore's Law is Dead (MLID), who can be hit and miss when it comes to accuracy, so take them with a grain of salt, especially as these are really early days to be discussing Zen 7. However, AMD has had some great success with its X3D chips that take advantage of TSMC's 3D silicon stacking tech, and it makes sense for the company to make more of it.

What is this 3D Core, then? "I assumed that meant V-cache, right? Just X3D cores," says MLID. "Well, actually, the answer is no. The answer here is that there is a new type of purely 3D Core that uses a radical new 3D stacking design for tons of cache and a ton of performance with core count increases."

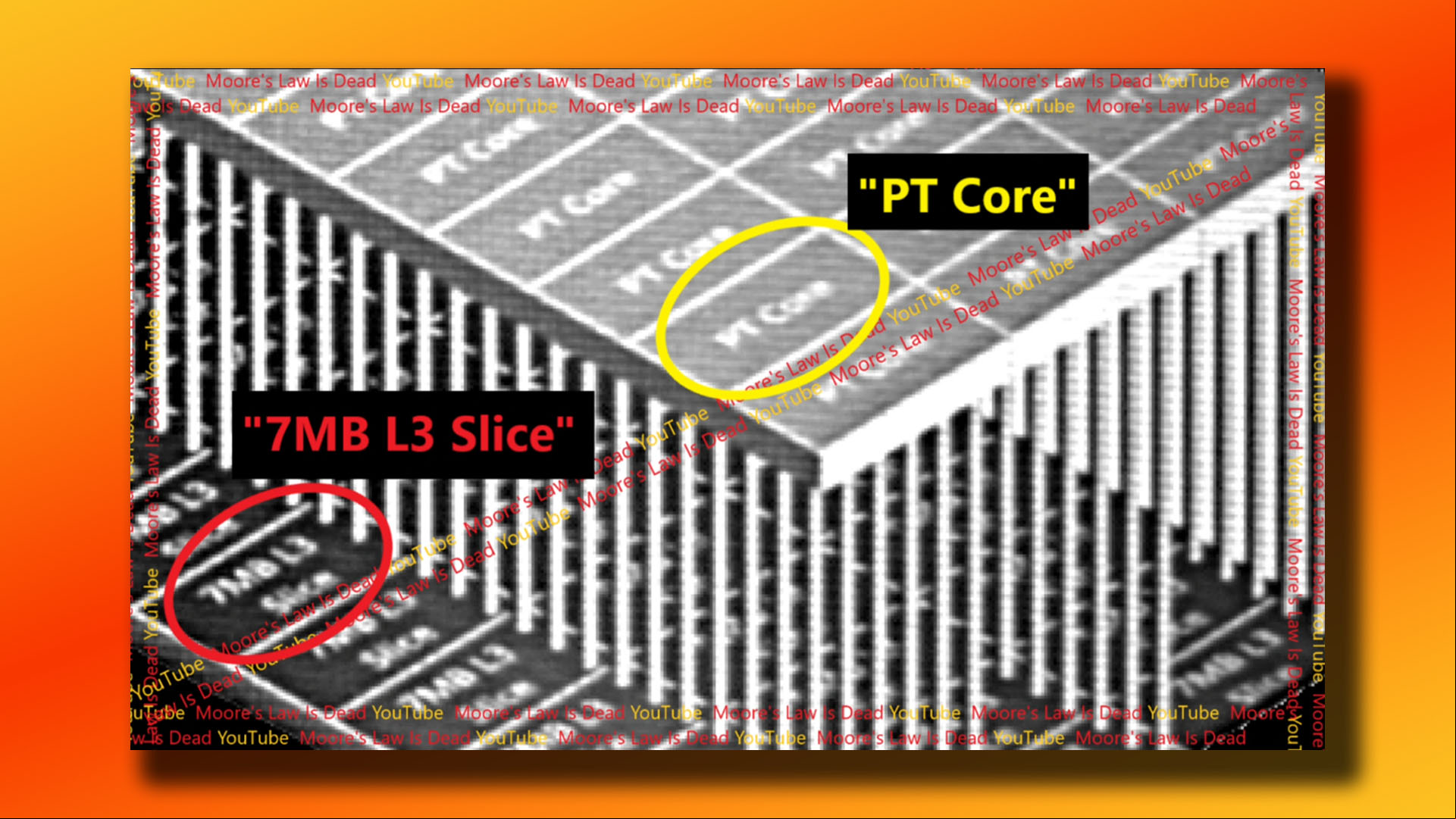

According to the leak, AMD Zen 7 core chiplets will be manufactured using TSMC's 1.4nm tech, which would be truly cutting-edge for the timeframe if this is true. However, AMD is reportedly going to stick with TSMC's 4nm process for making its 3D V-cache. MLID also shared what he claims is a part of a diagram showing the structure of a part of the Zen 7 architecture, which you can see below.

In it, you can see one layer contains many parts labeled "PT core" – with MLID claiming that a single Zen 7 chiplet could contain 33 of these PT cores. That's an odd number in more ways than one, which the YouTuber acknowledges, but sticks by it.

Meanwhile, directly under this layer of cores is another layer containing several 7MB slices of L3 cache, possibly one for each core. MLID discusses this tech in relation to AMD's EPYC Us, but AMD usually uses the same architectural designs across its whole product stack, and if this 3D Core is used in EPYC chips, there's also a good chance it will make it to Ryzen products too.

The idea behind this leaked design, according to MLID, is that 3D-stacking the L3 cache slices in this way reduces latency, though it would also massively decrease the space occupied by a chiplet and its cache on the package, while also potentially making sure that each core is able to directly access an enormous amount of cache.

Each core will reportedly also have 2MB of L2 cache on the die itself – double the amount found in current Zen 5 Us. If you put this tech in a Ryzen gaming U, you wouldn't need to worry about one core chiplet die not having access to the 3D V-cache, as in current Ryzen 9 X3D chips – every core could potentially have its own stack of L3 cache as standard, or there may be ways for the chip to see the whole lot as one giant pool as well.

According to MLID, AMD is looking to improve the instructions per clock (IPC) of its U cores by 15-25% with the move to Zen 7, while focusing on cutting-edge tech, with the aim of not being left behind by Intel again. Of course, we won't know how exactly this tech will work, or if it even exists, until AMD decides to lift the lid on Zen 7 itself, and that's a long way in the future. It's exciting to look at what might be on the cards, though.

If you're thinking of buying a new U right now, check out my how to install a U to make sure your upgrade goes smoothly.

You can also follow us on Google News for daily PC games news, reviews, and guides. In addition, we have a vibrant community Discord server, where you can chat about this story with of the team and fellow readers.